Invention Saves Consumers Trillions of Watt Hours and Millions of Dollars

San Diego, Sept. 6, 2011 -- A University of California, San Diego technology that significantly reduces the amount of energy wasted by chips in computers, mobile phones and other electronic devices has recently passed the trillion watt-hour milestone in energy savings, according to the technology’s current licensee, Tela Innovations. With residential energy costs at just over 11 cents per kilowatt hour, according to the latest figures from the U.S. Energy Information Administration, the savings are significant and growing, so far totaling well over $100 million that consumers haven’t been charged on their electricity bills.

|

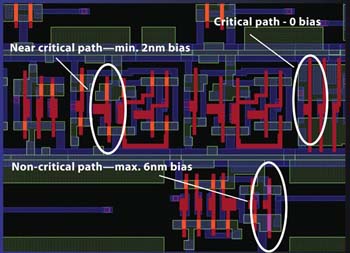

The technology, co-invented in 2003 by UC San Diego Jacobs School of Engineering Professor Andrew B. Kahng and his then-student Puneet Gupta, subtly modifies the dimensions of transistors, the tiny switches that control the flow of electricity in an integrated circuit. This approach, known as “gate-length biasing,” exploits the fact that slower transistors leak less power. The invention essentially ensures that transistors on a chip are as slow as possible without affecting performance.

Some of the fundamental concepts of the invention are now part of a broad, multi-university coalition funded by the National Science Foundation through a $10 million Expeditions in Computing grant awarded in 2010. UCLA's Puneet Gupta is a co-PI on the Variability-Aware Software for Efficient Computing with Nanoscale Devices project, and Kahng sits on the Advisory Board of the Variability Expedition, which is based in the California Institute for Telecommunications and Information Technology (Calit2).

The technology is now widely used in numerous applications such as network processors, Internet routers and the graphics processing units (GPUs) that are found in personal computers, tablets and game consoles.

|

Kahng and Gupta solved a complex optimization problem to identify which transistors can be slowed down. And they had to do this without changing the way chip designs are handed off from design teams to the silicon foundries that manufacture the chips.

“The key is figuring out which of the hundreds of millions of transistors on the chip to modify,” said Kahng. “Many, but not all, of the transistors can be made slower without affecting the clock frequency. We developed a tool to maximize leakage power savings without affecting product performance, and we created a flow to make this transparent and easy for both designers and manufacturers.

“As transistor dimensions continue to shrink in advanced manufacturing technologies, the potential for wasted energy only increases,” Gupta added “By adding even a few nanometers to the channel length of a transistor – using gate-length biasing – the invention substantially reduces leakage power while only slightly slowing down the transistor’s switching speed.”

|

As the technology is more widely deployed, the energy and cost savings continue to accelerate.

“Since the Blaze MO™ product was launched in 2006, energy consumption reductions – in products ranging from GPUs to mobile communication integrated circuits – achieved by our licensees using Tela’s patented Gate Length Biasing technology have conservatively amounted to over 1 trillion watt-hours,” said Rajiv Bhateja, Vice President of Power Optimization Products at Tela Innovations.

The gate-length biasing approach exemplifies the increasingly close coupling between design and manufacturing that is needed to keep Moore’s Law on track in today’s advanced technologies. Indeed, Kahng and his UC San Diego research lab, as well as Gupta and his UCLA research group, are widely recognized for pioneering work in the field known as “design for manufacturability,” meaning a device is designed to be easily manufacturable in order to maintain efficiency and reduce costs.

“Power has long been one of the key constraints for advanced chips, especially for mobile applications,” said Riko Radojcic, director at Qualcomm CDMA Technologies. “Qualcomm has been one of the early evaluation partners with Blaze technology, and demonstrated the leakage power reductions achieved by the Blaze optimization tool and gate-length biasing methodology on a baseband processor chip, starting at the 90nm technology node. It is gratifying to see such success for a technology that originated just a few miles away on the UC San Diego campus. I always look forward to the next ideas from Professors Kahng and Gupta.”

Media Contacts

Catherine Hockmuth, Jacobs School of Engineering, 858-822-1359, chockmuth@ucsd.edu

Related Links

Kahng Group at UCSD

Tela Innovations

UCSD Tech Transfer

Gupta NanoCAD Lab

Variability Expedition